visual

SCROLL

introduction

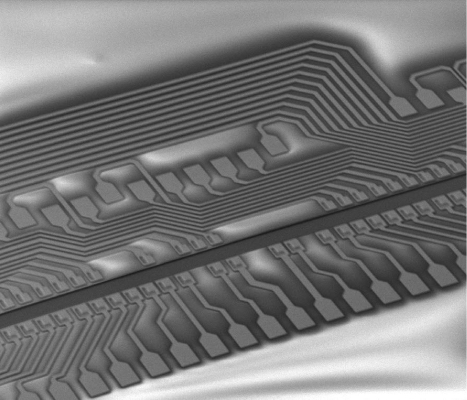

晶圆级封装状态下对晶元进行封装和测试后,

切割芯片制作完成品的技术 WLCSP

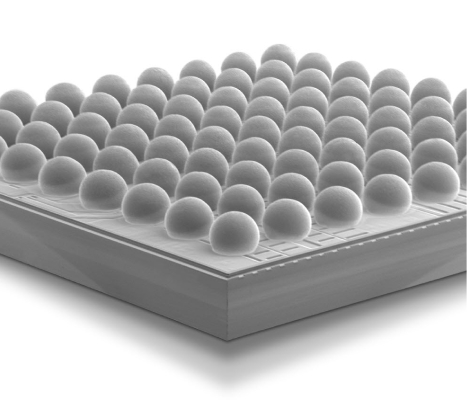

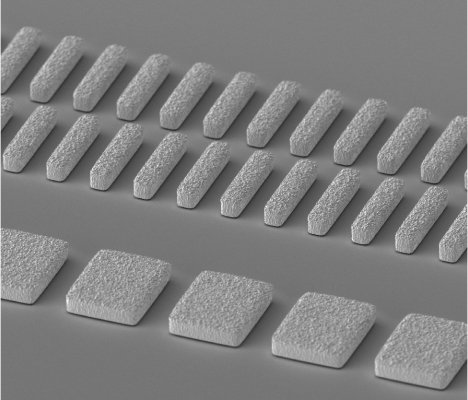

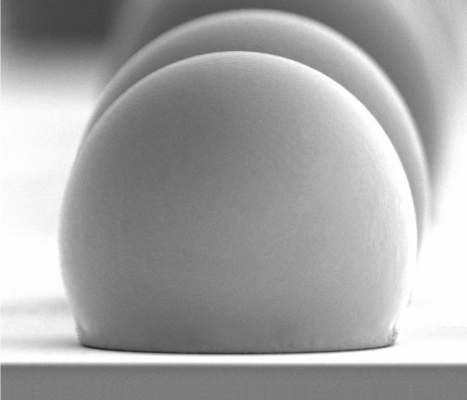

不同于以往的加工晶元后,一一切割芯片后,再进行封装的传统方式。晶圆级封装(Wafer Level Package) WLCSP将晶元进行封装和测试后,切割芯片,将完成品制作而成,是可实现芯片最小化的封装方法。WLCSP不仅可将芯片封装大小与芯片大小一致,还具备优秀的导电特性及较高的价格竞争力,得益于此,移动市场需求与日俱增,适用本技术的产品不断增多。如今,公司为满足客户需求,提供从2 layer至6 layer多样结构的WLCSP服务。

Application

-

PMIC

-

RF & BB SoC

-

Transceiver

-

AOC

-

Sensors

Process Capability

-

Bumping

-

01.

8inch and 12inch Available

-

02.

WLCSP Structural Option

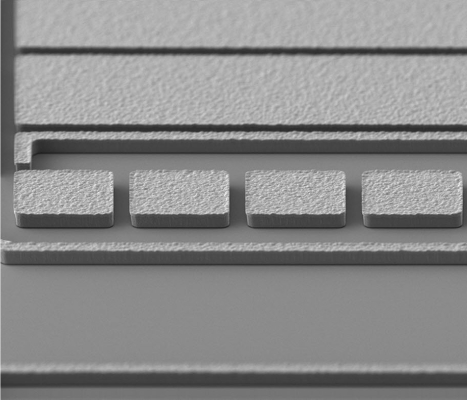

- 1P1M

- 2P2M (Single RDL with UBM)

- 3P3M (Dual RDL)

-

03.

Ball Pitch

- 0.3, 0.35, 0.4, 0.5mm

-

04.

Ball Height

- Ball drop : > 0.15mm

- Electroplated : < 0.11mm (Lead free, SnAg 1.8%)

-

05.

Re-PSV Material Option

- High temperature curable Polyimide

- Low temperature curable Polyimide

-

06.

Re-PSV Thickness

- 5 to 20um

-

07.

Re-PSV Opening Diameter

- Min. diameter : 25um

-

08.

RDL Thickness

- 3 to 10um (20um under development)

-

09.

RDL Width / Space (min)

- 12/12um

-

01.

-

Backend

-

01.

Back-Grinding for Wafer Thinning (min)

- >150um

-

02.

Backside Coating

- Available

-

03.

Scribe Lane for Dicing (min)

- 60um (Laser Grooving Available_80um)

-

04.

Die size (min) available for TnR

- 0.5x0.5mm

-

05.

Inspection

- Post Sawing AOI, 6side Inspection @ TnR

-

01.

introduction

用金子凸块处理,具有高强I/O、连接灵活、

轻薄等特征的晶圆技术 Au Bump

用金子凸块处理的晶元利用于安装在普通消费品的COG (Chip on Glass), COF(Chip on Film), COP(Chip on Plastic)封装。

这一技术为了取代wire bond技术而诞生。用金子凸块的晶元通过热压缩完成贴附与封装表面。

由于对具备高强I/O、灵活的连接性与轻薄优势的封装需求与日俱增,以金子凸块处理芯片将会成为利用于携带式产品中的最佳选择。

Application

-

COF and COG PKG for TV

-

Monitor

-

Notebook DDIC

-

Mobile

-

Tablet

-

Automotive DIC

Process Capability

-

Au Bumping

-

01.

8inch and 12inch Available

-

02.

Various Hardness Available from 50Hv Up to 90Hv

-

03.

Bump Height (Typical)

- 8 to 16um

-

04.

Height Uniformity

- WID : ≤ 2um

- WIW : ± 2um

-

05.

Bump Pitch (min)

- Straight 21um

-

06.

BOA(Bump On Active circuit) Structure Qualified

-

07.

2D, 3D AOI

-

01.

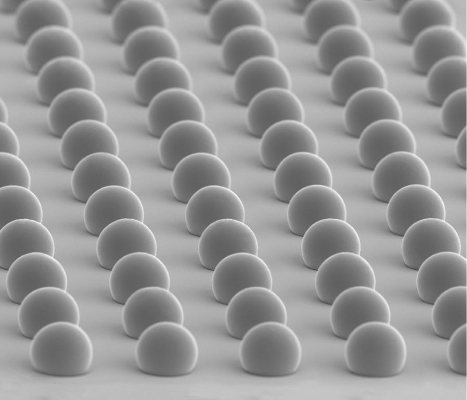

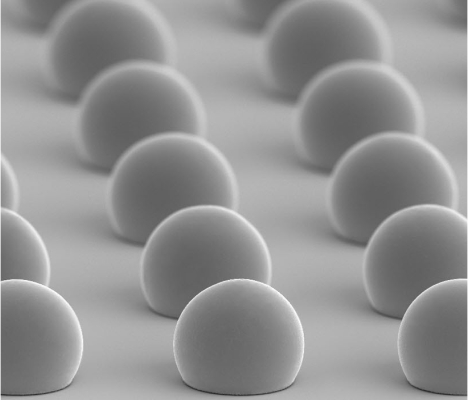

introduction

利用于COC, fcBGA,

fcQNF等多种flip chip封装的技术

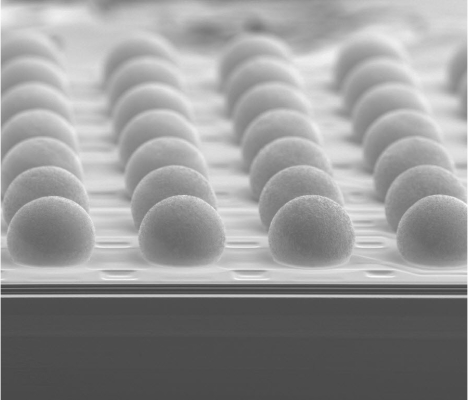

Solder Bump

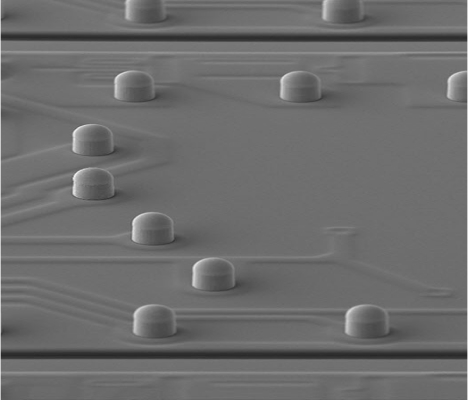

Solder bump利用于 COC, fcBGA, fcQNF等多种flip chip封装工艺中。

如今,LBSemicon支持fine pitch的Lead free solder bump工艺。

用于QFN的晶元和基板位置不适合flip chip封装的产品,通过RDL,不必改变基板格式,可实现flip chip封装。

Application

-

fcBGA PKG for AP

-

SoC

-

PMIC

-

Graphics

Process Capability

-

Bumping

-

01.

8inch and 12inch Available

-

02.

Solder Bump Structural Option

- 1M (Direct Solder Bump on Fab-Passivation)

- 1P1M (Solder Bump on Polymeric Re-Passivation)

- 2P2M (Solder Bump with Electroplated Cu RDL)

-

03.

Solder Bump Pitch and Height

- Bump Pitch (min) : 140um

- Bump height : 50 to 110um (Depending on Bump Diameter and Pitch)

-

04.

Solder Material Option

- Lead Free SnAg (Ag1.8wt%)

-

05.

Re-Passivation Option

- High Temperature Curable Polyimide

- Low Temperature Curable Polyimide

-

01.

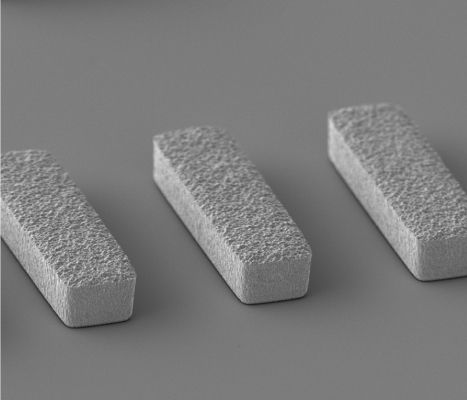

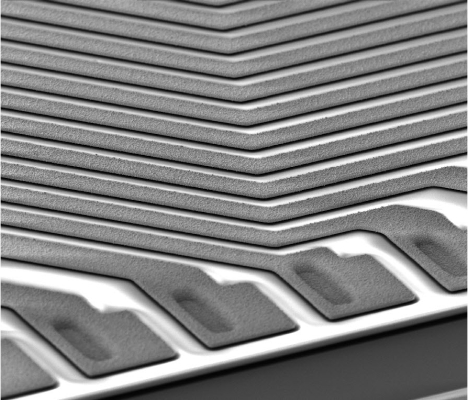

introduction

可实现pitch低于40um,

被广泛利用的Bumping技术

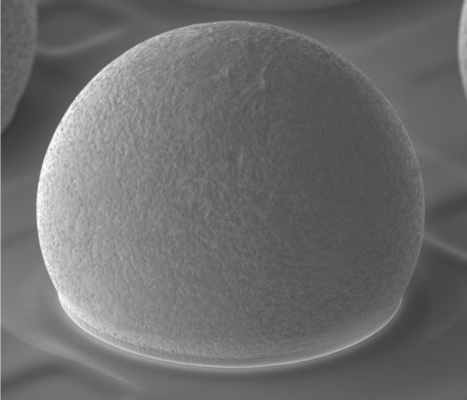

Cu Pillar bump

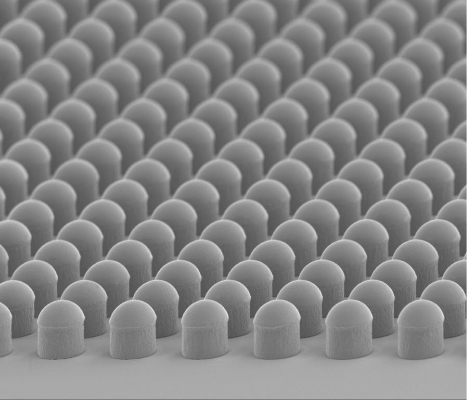

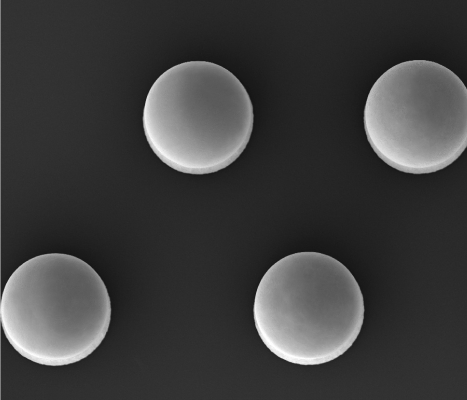

半导体元件不断实现的高性能、高密度,随之芯片I/O的密度急速增加,相应要求的凸块pitch不断缩短。顺应对fine pitch的新要求,Cu pillar作为 bumping技术研发而成。 原有的Solder bump可实现的最短pitch为150um,而Cu pillar可实现pitch低于40um的高密度封装。不仅如此,与solder bump相比,放热性更加,电子移动性更强,如今被广为利用,其今后的市场前景也十分明朗。

Application

-

fcBGA and fcQFN PKG for RFIC

-

BB & AP Processor

-

Power Amplifiers

-

NAND Flash

-

WiFi Module

Process Capability

-

Bumping

-

01.

8inch and 12inch Available

-

02.

Cu Pillar Structural Option

- 1M (Direct CuP on Fab-Passivation)

- 1P1M (CuP on Polymeric Re-Passivation)

- 1P2M (Both RDL First and PI First Available)

- 2P2M (CuP with Electroplated Cu RDL)

-

03.

Cu Pillar Pitch and Height

- Pitch (min): 50um Pitch for 8inch / 40um Pitch for 12inch

- Total CuP Height : 30 ~ 90um (Depending on Cu Pillar Diameter and Pitch)

-

04.

Cu Pillar Material Stack-up Option

- Cu Post / Solder Cap

- Cu Post / Ni Barrier Metal / Solder Cap

-

05.

Solder Cap Material Option

- Lead Free SnAg (Ag1.8wt%)

-

01.

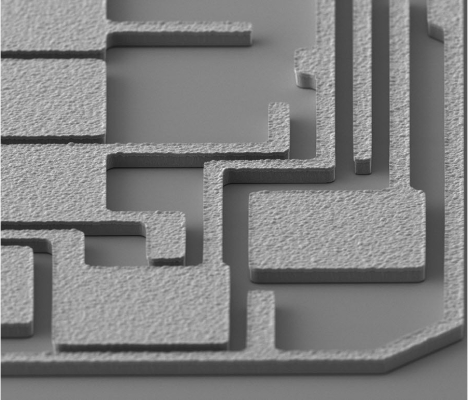

introduction

无需改变存储终端基板的格式,

通过重新布置基板位置,实现SIP,

最终轻松完成stack die wire bonding的技术

Au RDL

Au RDL一般用于重组 I/O基板格式,以便利用于wire bonding package。 Au RDL提供卓越的wire bond-ability和高信任度,利用Au RDL,无需改变存储终端基板的格式,通过重新布置基板位置,实现SIP,最终便捷轻松地完成stack die wire bonding。

Application

-

Mostly used for Multi stack Wire bonding PKG for Memory such as NAND Flash and DRAM

-

Available for all applications that need Au wire bonding

Process Capability

-

Bumping

-

01.

8inch and 12inch Available

-

02.

Au RDL Structural Option

- 1P1M (Au RDL on Polymeric Re-Passivation)

- 2P1M (Additional Polymeric Re-Passivation Over RDL)

-

03.

Au RDL Thickness

- 3 to 5um by Electroplating

-

04.

Au RDL Width / Space

- 15 / 15um

-

05.

Re-Passivation

- Low Temperature Curable Polyimide

-

01.

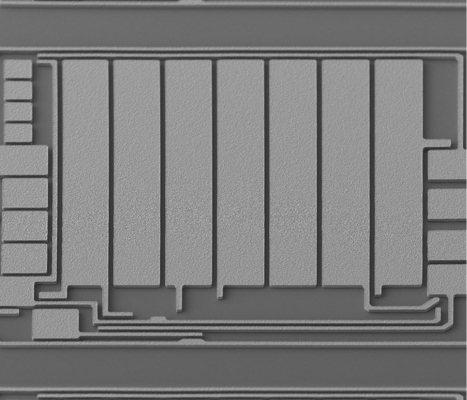

introduction

无需在下面另加聚合物保护层,

可在fab passivation直接快速进行的技术

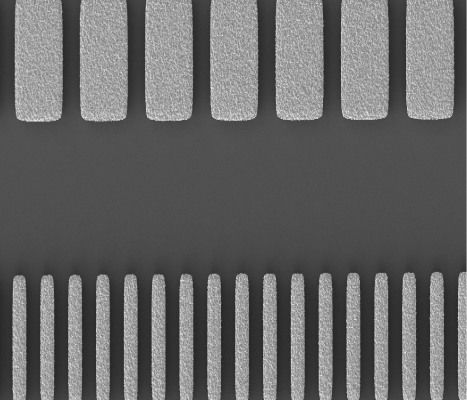

Thick Cu

Thick Cu工艺无需在下面另加聚合物保护层,可在fab passivation直接快速进行。

在Thick Cu工艺中,由于铜阻力低,其导电率高于一般的铝,厚厚的铜在键合(bonding)工艺中,可吸收大量压力,提供宽广的键合工艺窗口,并利用Au, pure, Pd/Cu等多样wire,无裂缝,

稳定实现BOAC工序。

* BOAC : a layout technology called “Bond Over Active Circuit”

Application

-

Wire bonding PKG for Power Management IC and Memory

Process Capability

-

Bumping

-

01.

8inch Available

-

02.

Thick Cu Structural Option

- 1M (Direct Thick Cu on Fab-Passivation)

- 1P1M (Direct Thick Cu + Additional Polymeric Re-Passivation Over Thick Cu)

- 1P1M (Thick Cu on Polymeric Re-Passivation)

-

03.

Thick Cu Thickness

- 5 to 10um

-

04.

Thick Cu Stack-up Material : Electroplated Cu/Ni/Au

- Cu for Rs Reduction

- Ni for Diffusion Barrier

- Au for Wire Bonding ( Au and Cu Wire Bonding Available)

-

05.

Thick Cu Width / Space

- 12/12um

-

06.

Re-Passivation Option

- High Temperature Curable Polyimide

- Low Temperature Curable Polyimide (Under Qualification)

-

01.

introduction

将带导电Bump的Driver IC直接连接到

Glass Panel上的Bonding技术, COG

COG是Chip On Glass的缩写, 是在Wafer状态下将带导电Bump的Driver IC直接连接到Glass Panel上的Bonding技术。它被广泛应用于高分辨率LCD, OLED产品.

Process

-

01

Laminating

晶元研磨(Wafer Grinding),保护回路表面,避免晶元受损,在图形表面贴附保护胶带的工艺

-

02

Back Grinding

为满足客户对产品规格轻薄短小化的需求,利用叶轮研磨晶元内面的工艺

-

03

Laser Marking

为了实现芯片跟踪,利用激光在晶元里各个芯片上刻印固有代码的工艺

-

04 Option

Laser Grooving

使用激光去除难切削材料Low-K Layer和Metal Layer的工艺

-

05

SAW

根据规定的芯片尺寸将带装晶圆切割成单个芯片的工艺

-

06 Option

Laser Grooving

使用等离子体去除晶圆表面灰尘颗粒的工艺

-

07

Post AVI

对切割完晶圆进行外观检查的工艺

-

08

UV Irradiation

为使切割芯片拾取更加容易,降低UV胶带粘合力的工艺

-

09

Pick & Place

晶圆切割完之后,将合格的芯片移至规定托盘的工艺

-

10

AVI

对在托盘里装好的芯片进行外观检查的工艺

-

11

Visual Inspection

根据移至芯片载体(托盘)的合格芯片外观检查标准,区分合格芯片与不合格芯片的工艺

-

12

Packing

最终选出的合格芯片出货之前,对其进行真空包装、内包装、外包装的工艺

introduction

晶圆级封装状态下对晶元进行封装和测试后,

切割芯片制作完成品的技术 WLCSP

Process

-

01

Laminating

晶元研磨(Wafer Grinding),保护回路表面,避免晶元受损,在图形表面贴附保护胶带的工艺

-

02

Back Grinding

为满足客户对产品规格轻薄短小化的需求,利用Grinding Wheel研磨晶圆背面的工艺

-

03

Back Side Coating

在晶圆背面涂上特殊薄膜以保护芯片免受外部冲击的工艺

-

04

Laser Marking

为了实现芯片跟踪,利用激光在晶圆各个芯片上刻印固有代码的工艺

-

05

Foil Mount

使用Tape将Frame和晶圆粘合在一起以促进Sawing的工艺

-

06 Option

Laser Grooving

使用激光去除难切削材料Low-K Layer和Metal Layer的工艺

-

07

SAW

根据规定的芯片尺寸将带装晶圆切割成单个芯片的工艺

-

08

Post AVI

对切割完晶圆进行外观检查的工艺

-

09

UV Irradiation

为使切割芯片拾取更加容易,降低UV胶带粘合力的工艺

-

10

Tape & Reel

切割完的芯片中,取出良品芯片装进卷里的工艺

-

11

Visual Inspection

根据移至芯片载体(托盘)的合格芯片外观检查标准,区分合格芯片与不合格芯片的工艺

-

12

Packing

最终选出的合格芯片出货前,对其进行真空包装、内包装、外包装的工艺

introduction

通过晶圆级的各种测试来检查每个芯片的状态

Chip Probe Test

LB Semicon 的 EDS(Electrical Die Sorting)是检查单个芯片的质量特性是否达到目标水平的工艺。通过良品/次品芯片的分选、设计阶段的问题修正、以及次品芯片的提前分选,可以提高后续工艺的工作效率。

我们根据半导体芯片的用途对器件类型进行分类,并使用适合每个芯片特性的专用测试仪对芯片进行电气性能和质量检查。在此过程中,可以使用Auto Wafer Prober自动、安全、快速地测试单个芯片。

测试可分为:温度测试、速度测试和操作测试。

温度测试是在低温(Cold,-40℃)到高温(Hot,125℃)的条件下应用和测试的,因为它们在使用实际芯片时必须在各种温度环境下运行。

速度测试测量产品的运行速度。半导体本身的运行速度很重要,但与外围设备的通信速度也很重要,因此在满足芯片规格的各种环境下测试速度至关重要。

操作测试包括直流、交流和功能测试,每个测试验证每个芯片的电流或电压、模拟特性和操作状态。

-

01 IAQ

-

02 P-TEST

-

03 INKING

-

04 SCOPE V/I

-

05 DOC.

INSPECTION -

06 QC GATE

(OGI) -

07 PACKING

(QPI) -

08 Shipping &

Back-end

Features

请左右切换画面确认。| Application | Vendor | Model |

Specification (Pin mux, Pattern mux) |

Remark |

|---|---|---|---|---|

| DDI | Advantest | T6372(ND2) | 437.5MHz | - |

| T6373(ND3) | 437.5MHz | HSIF : 1.25GHz | ||

| T6391(ND4C) | 800MHz | UHSIF : 1.35GHz ~ 2.0GHz(License) | ||

| T6391S(ND4ST) | 800MHz | UHSIF : 2.0GHz ~ 3.25GHz(License) | ||

| Yokogawa | TS670 | - | UVI : 2.0A | |

| ST6730A | 375MHz | NSIO | ||

| ST6731A | 1.25GHz | GSIO | ||

| PMIC | Eagle | ETS-364B | 66MHz | - |

| Advantest | T2000-IPS | 250MBps | - | |

| T2000-IPS/EPP | 250Mbps/800Mbps/1Gbps | - | ||

| T2000-IPS 52TH | 1Gbps | GPWGD | ||

| CIS | Advantest | T2000-ISS/32 | 800Mbps | 1.2G Capture Module |

| T2000-ISS/64P | 1Gbps | 4.8G Capture Module | ||

| SOC | Teradyne | Ultra-FLEX | 1600Mbps | - |

Re-configuration Process

切割后的芯片,若发生 Sorting Issue或需要 Test Program Debugging Re-Test时,在尽可能缩小损失的前提下,可进行Wafer Level Chip Test

- Chip on Tray

- Chip on Blue Tape(Ring Frame)

- Re-Test

- 2200 evo-Key Features(Re-con)

- Specifications FP 3000(Test)

DDI Test System

DDI Test System

DDI Test System

DDI Test System

PMIC Test System

PMIC Test System

CIS Test System

CIS Test System

SoC Test System

SoC Test System