visual

SCROLL

introduction

웨이퍼 상태에서

한번에 패키지 공정 및 테스트를 진행한 후

칩을 절단하여 완제품을 만들어 내는 기술 WLCSP

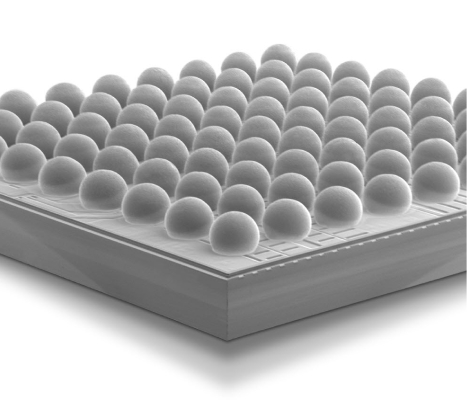

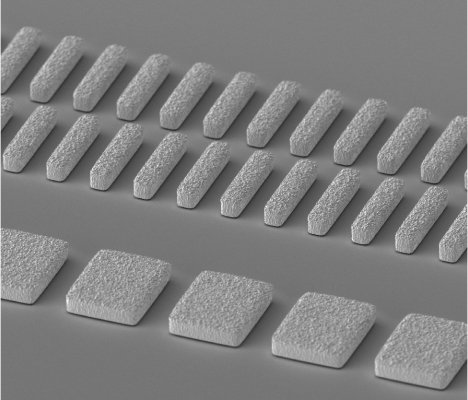

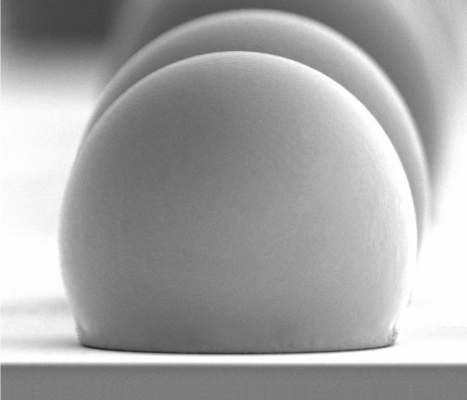

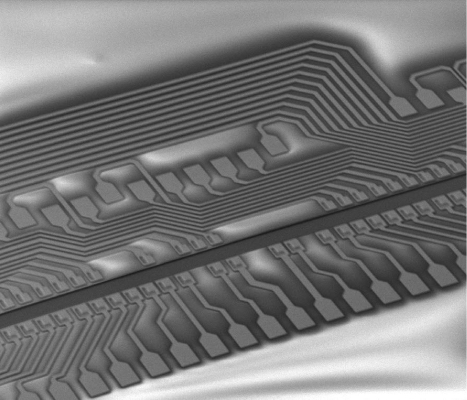

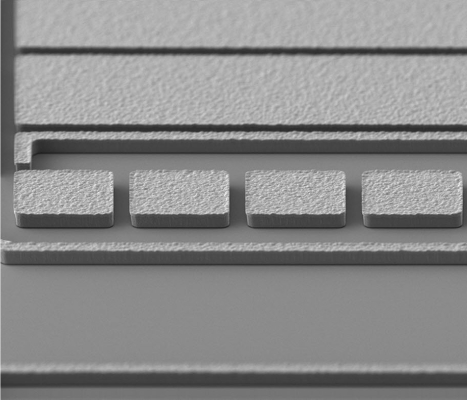

웨이퍼 레벨 패키지(Wafer Level Package) WLCSP는 웨이퍼 가공 후 하나씩 칩을 잘라내 패키징하던 기존 방식과 달리,

웨이퍼 상태에서 한번에 패키지 공정 및 테스트를 진행한 후 칩을 절단하여 완제품을 만들어 내는 기술로

가장 작은 크기를 구현할 수 있는 칩 크기의 패키지 방법입니다.

WLCSP는 칩 크기와 동일한 크기의 패키지 사이즈 구현이 가능할 뿐 아니라

우수한 전기적 특성과 높은 가격 경쟁력으로 인해 모바일 시장에서의 수요가 더욱 증가하고 있으며,

적용 제품군 또한 점차 확대되고 있으며, 현재 LB세미콘에서는 고객의 요구에 맞춰 2 layer부터 6 layer까지

다양한 구조의 WLCSP를 서비스하고 있습니다.

Application

-

PMIC

-

RF & BB SoC

-

Transceiver

-

AOC

-

Sensors

Process Capability

-

Bumping

-

01.

8inch and 12inch Available

-

02.

WLCSP Structural Option

- 1P1M

- 2P2M (Single RDL with UBM)

- 3P3M (Dual RDL)

-

03.

Ball Pitch

- 0.3, 0.35, 0.4, 0.5mm

-

04.

Ball Height

- Ball drop : > 0.15mm

- Electroplated : < 0.11mm (Lead free, SnAg 1.8%)

-

05.

Re-PSV Material Option

- High temperature curable Polyimide

- Low temperature curable Polyimide

-

06.

Re-PSV Thickness

- 5 to 20um

-

07.

Re-PSV Opening Diameter

- Min. diameter : 25um

-

08.

RDL Thickness

- 3 to 10um (20um under development)

-

09.

RDL Width / Space (min)

- 12/12um

-

01.

-

Backend

-

01.

Back-Grinding for Wafer Thinning (min)

- >150um

-

02.

Backside Coating

- Available

-

03.

Scribe Lane for Dicing (min)

- 60um (Laser Grooving Available_80um)

-

04.

Die size (min) available for TnR

- 0.5x0.5mm

-

05.

Inspection

- Post Sawing AOI, 6side Inspection @ TnR

-

01.

introduction

웨이퍼 상태에서

금으로 Bumping 처리하여 높은 I/O와 유연한 연결성,

얇고 가벼운 특성을 갖는 웨이퍼 공정 기술

Au Bump

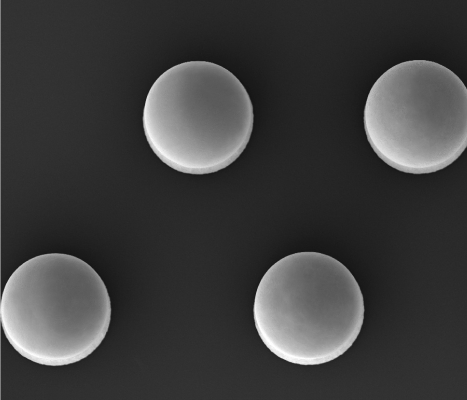

금으로 범핑 처리된 웨이퍼는 보통 소비재에 적용되는 COG (Chip on Glass), COF(Chip on Film),

COP(Chip on Plastic) 패키지에 사용됩니다. Au Bump는 wire bond 기술을 대체하기 위해 개발되었으며

금으로 범핑된 칩은 열적 압축 방식을 통하여 패키지에 장착됩니다.

높은 I/O와 유연한 연결성 뿐만 아니라 얇고 가벼운 특성을 갖는 패키지에 대한 수요가 증가하고 있기 때문에,

금으로 범핑 처리된 웨이퍼들은 이러한 휴대용 제품들에 더욱 더 적합한 방식이 될 것입니다.

Application

-

COF and COG PKG for TV

-

Monitor

-

Notebook DDIC

-

Mobile

-

Tablet

-

Automotive DIC

Process Capability

-

Au Bumping

-

01.

8inch and 12inch Available

-

02.

Various Hardness Available from 50Hv Up to 90Hv

-

03.

Bump Height (Typical)

- 8 to 16um

-

04.

Height Uniformity

- WID : ≤ 2um

- WIW : ± 2um

-

05.

Bump Pitch (min)

- Straight 21um

-

06.

BOA(Bump On Active circuit) Structure Qualified

-

07.

2D, 3D AOI

-

01.

introduction

COC, fcBGA, fcQNF 등

다양한 flip chip 패키지에 활용하는 기술 Solder Bump

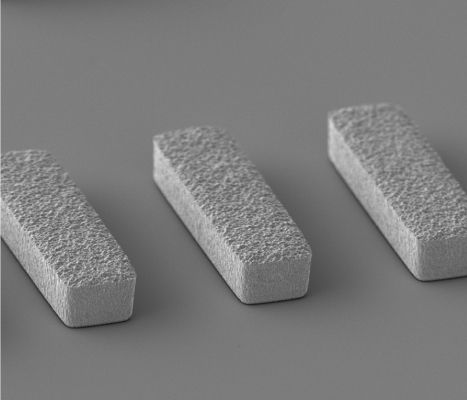

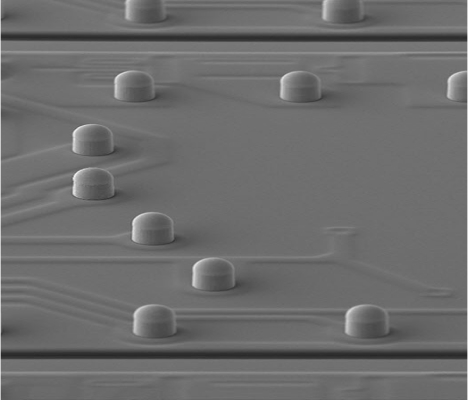

Solder bump는 COC, fcBGA, fcQNF 등 다양한 flip chip 패키지에 활용되고 있습니다.

현재 LB세미콘에서는 fine pitch의 Lead free solder bump 공정을 서비스하고 있으며,

QFN용으로 제작한 웨이퍼와 같이 패드 위치가 flip chip 패키지에 적합하지 않은 제품도 RDL 공정을 통해

패드 레이아웃 변경 없이 filp chip 패키지가 가능합니다.

Application

-

fcBGA PKG for AP

-

SoC

-

PMIC

-

Graphics

Process Capability

-

Bumping

-

01.

8inch and 12inch Available

-

02.

Solder Bump Structural Option

- 1M (Direct Solder Bump on Fab-Passivation)

- 1P1M (Solder Bump on Polymeric Re-Passivation)

- 2P2M (Solder Bump with Electroplated Cu RDL)

-

03.

Solder Bump Pitch and Height

- Bump Pitch (min) : 140um

- Bump height : 50 to 110um (Depending on Bump Diameter and Pitch)

-

04.

Solder Material Option

- Lead Free SnAg (Ag1.8wt%)

-

05.

Re-Passivation Option

- High Temperature Curable Polyimide

- Low Temperature Curable Polyimide

-

01.

introduction

40um 이하 피치의 고밀도 패키지 구현이 가능하여

다양한 패키지에서 이용되고 있는 Bumping 기술

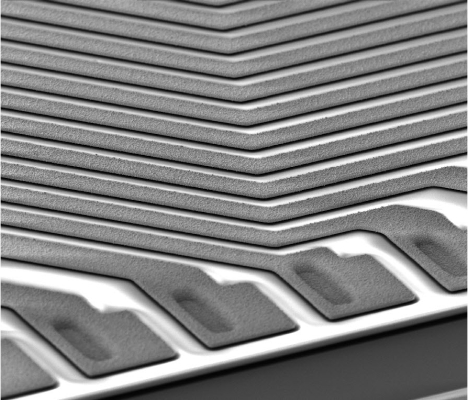

Cu Pillar bump

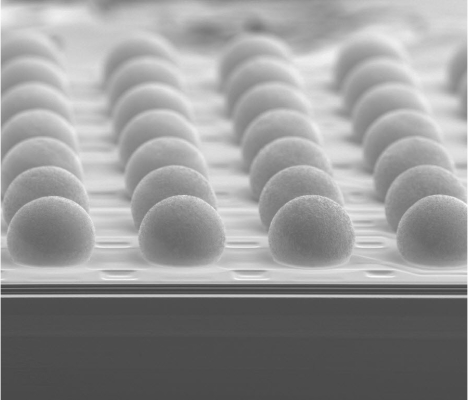

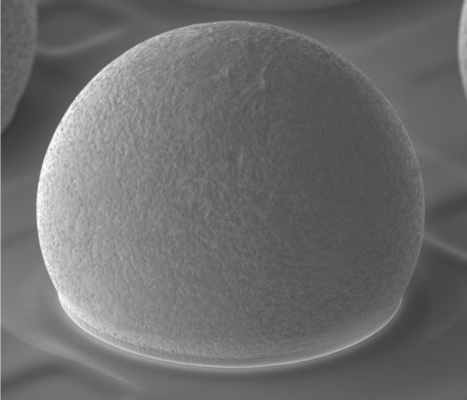

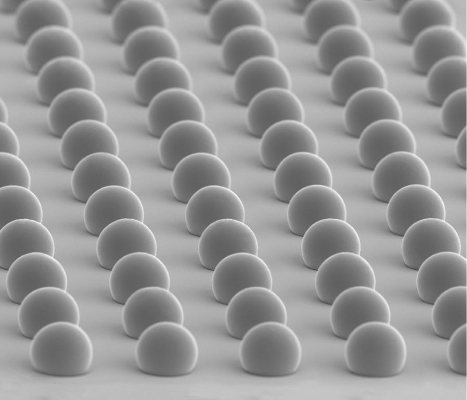

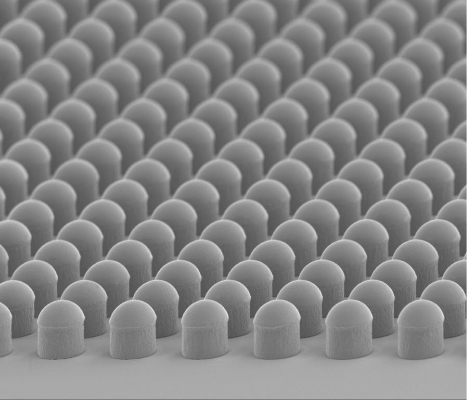

반도체 소자의 고성능화, 고밀도화가 급격히 진행됨에 따라 칩의 I/O 밀도가 급속히 증가하며 있습니다.

그에 상응하여 요구되는 범프의 pitch도 지속적으로 감소하고 있습니다.

Cu pillar는 이러한 fine pitch 요구에 대응하기 위해 개발된 bumping 기술입니다.

전통적인 Solder bump의 경우 대응 가능한 최소 pitch가 150um 수준인데 반해

Cu pillar는 40um 이하 피치의 고밀도 패키지 구현이 가능합니다.

또한 Solder bump 대비 우수한 열방출 성능과 Electromigration 특성으로 인해

이미 Cu pillar는 다양한 패키지에 이용되고 있으며 앞으로 그 활용도는 더욱 높아질 전망입니다.

Application

-

fcBGA and fcQFN PKG for RFIC

-

BB & AP Processor

-

Power Amplifiers

-

NAND Flash

-

WiFi Module

Process Capability

-

Bumping

-

01.

8inch and 12inch Available

-

02.

Cu Pillar Structural Option

- 1M (Direct CuP on Fab-Passivation)

- 1P1M (CuP on Polymeric Re-Passivation)

- 1P2M (Both RDL First and PI First Available)

- 2P2M (CuP with Electroplated Cu RDL)

-

03.

Cu Pillar Pitch and Height

- Pitch (min): 50um Pitch for 8inch / 40um Pitch for 12inch

- Total CuP Height : 30 ~ 90um (Depending on Cu Pillar Diameter and Pitch)

-

04.

Cu Pillar Material Stack-up Option

- Cu Post / Solder Cap

- Cu Post / Ni Barrier Metal / Solder Cap

-

05.

Solder Cap Material Option

- Lead Free SnAg (Ag1.8wt%)

-

01.

introduction

메모리 디바이스의 패드 레이아웃 설계 변경 없이 보다

쉽고 편리하게 stack die wire bonding이 가능하도록

패드 위치를 재배열해 SIP를 구현하는 기술 Au RDL

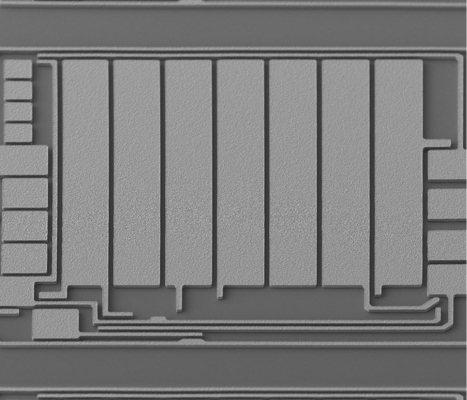

Au RDL은 대부분 wire bonding package에 적합하게 만들기 위해 I/O 패드의 레이아웃을 재위치 시키는데 쓰입니다.

Au RDL은 우수한 wire bond-ability와 높은 신뢰성을 제공하며, Au RDL을 이용하여

메모리 디바이스의 패드 레이아웃 설계 변경 없이 보다 쉽고 편리하게 stack die wire bonding이 가능하도록

패드 위치를 재배열해 SIP를 구현합니다.

Application

-

Mostly used for Multi stack Wire bonding PKG for Memory such as NAND Flash and DRAM

-

Available for all applications that need Au wire bonding

Process Capability

-

Bumping

-

01.

8inch and 12inch Available

-

02.

Au RDL Structural Option

- 1P1M (Au RDL on Polymeric Re-Passivation)

- 2P1M (Additional Polymeric Re-Passivation Over RDL)

-

03.

Au RDL Thickness

- 3 to 5um by Electroplating

-

04.

Au RDL Width / Space

- 15 / 15um

-

05.

Re-Passivation

- Low Temperature Curable Polyimide

-

01.

introduction

별도의 하부 폴리머 보호층 없이

fab passivation에 바로 형성하는 기술 Thick Cu

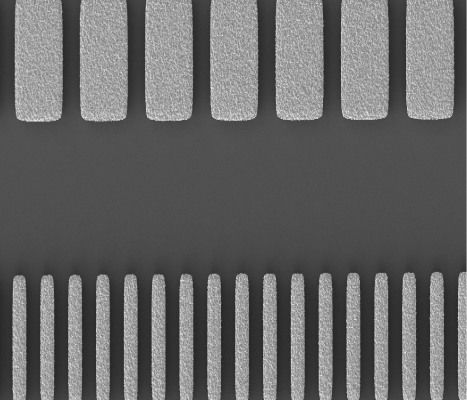

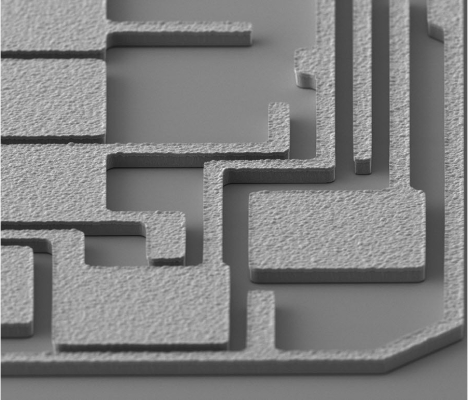

Thick Cu 공정은 별도의 하부 폴리머 보호층 없이 fab passivation에 바로 형성됩니다.

구리의 낮은 저항으로 인해 일반적인 알루미늄 배선에 비해 높은 전류효율을 제공하며,

두꺼운 구리가 본딩 공정에서 상당한 응력(stress)를 흡수할 수 있어 넓은 bonding process window를 제공할 뿐 아니라

Au, pure, Pd/Cu등 다양한 wire을 사용하여 crack 우려 없이 안정적으로 BOAC 공정이 가능합니다.

* BOAC : a layout technology called “Bond Over Active Circuit”

Application

-

Wire bonding PKG for Power Management IC and Memory

Process Capability

-

Bumping

-

01.

8inch Available

-

02.

Thick Cu Structural Option

- 1M (Direct Thick Cu on Fab-Passivation)

- 1P1M (Direct Thick Cu + Additional Polymeric Re-Passivation Over Thick Cu)

- 1P1M (Thick Cu on Polymeric Re-Passivation)

-

03.

Thick Cu Thickness

- 5 to 10um

-

04.

Thick Cu Stack-up Material : Electroplated Cu/Ni/Au

- Cu for Rs Reduction

- Ni for Diffusion Barrier

- Au for Wire Bonding ( Au and Cu Wire Bonding Available)

-

05.

Thick Cu Width / Space

- 12/12um

-

06.

Re-Passivation Option

- High Temperature Curable Polyimide

- Low Temperature Curable Polyimide (Under Qualification)

-

01.

introduction

Wafer 상태에서 IC Pad 위에 도전성 Bump를

형성시킨 Driver IC를 Glass Panel 위에

직접 접속시키는 Bonding 기술 COG

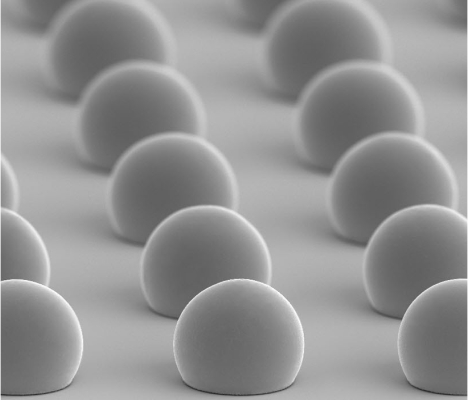

COG는 Chip On Glass의 약자로, Wafer 상태에서 IC Pad 위에 도전성 Bump를 형성시킨 Driver IC를

Glass Panel 위에 직접 접속시키는 Bonding 기술로써, 고해상도 (High Resolution) LCD, OLED 제품에 적용됩니다.

Process

-

01

Laminating

Wafer Grinding시 Wafer 회로면을 보호하고 Wafer Broken 방지를 위해 보호Tape를 패턴면에 접착하는 공정

-

02

Back Grinding

경박단소 고객사양을 만족시키기 위해 Wafer 이면을 Grinding wheel를 이용하여 연마하는 공정

-

03

Laser Marking

Chip Trace을 위해 Laser를 이용하여 각각 Chip에 고유 Code를 각인하는 공정

-

04 Option

Laser Grooving

Laser를 이용하여 난삭재인 Low-K Layer 와 Metal Layer를 제거하는 공정

-

05

SAW

ape Mount된 Wafer를 규정된 Chip Size 기준, 개별 Chip으로 절단하는 공정

-

06 Option

Plasma

Wafer 표면의 유기물을 Plasma를 이용하여 제거하는 공정

-

07

Post AVI

SAW공정 완료된 Wafer의 외관 검사 공정 (Chipping and Surface Damage Inspection)

-

08

UV Irradiation

원활한 Pick-up를 위해 UV Tape의 접착력을 저하시키는 공정

-

09

Pick & Place

SAW된 Wafer에서 양품 Chip만 TRAY에 담는 공정

-

10

AVI

TRAY에 담긴 Chip에 대한 외관검사 공정

-

11

Visual Inspection

Chip Carrier(Tray)에 옮겨 담은 양품chip의 외관 검사 기준에 의거, 양/불 분류하는 공정

-

12

Packing

최종 분류된 양품Chip의 출하를 위한 진공포장, 내포장, 외포장을 하는 공정

introduction

웨이퍼 상태에서 한번에 패키지 공정 및

테스트를 진행한 후 칩을 절단하여 완제품을

만들어 내는 공정 WLCSP

Process

-

01

Laminating

Wafer Grinding시 Wafer 회로면을 보호하고 Wafer Broken 방지를 위해 보호Tape를 패턴면에 접착하는 공정

-

02

Back Grinding

경박단소 고객사양을 만족시키기 위해 Wafer 이면을 Blade wheel를 이용하여 연마하는 공정

-

03

Back Side Coating

외부 충격으로부터 chip를 보호하기 위해 Wafer 이면에 특수한 Film를 도포하는 공정

-

04

Laser Marking

Chip Trace을 위해 Laser를 이용하여 각각 Chip에 고유 Code를 각인하는 공정

-

05

Foil Mount

Sawing공정 진행을 위하여 Tape를 이용, Frame과 Wafer를 접착 시키는 공정

-

06 Option

Laser Grooving

Laser를 이용하여 난삭재인 Low-K Layer 와 Metal Layer를 제거하는 공정

-

07

SAW

Tape Mount된 Wafer를 규정된 Chip Size 기준, 개별 Chip으로 절단하는 공정

-

08

Post AVI

SAW공정 완료된 Wafer의 외관 검사 공정 (Chipping and Surface Damage Inspection)

-

09

UV Irradiation

원활한 Pick-up를 위해 UV Tape의 접착력을 저하시키는 공정

-

10

Tape & Reel

SAW된 Wafer에서 양품 Chip만 Reel에 담는 공정

-

11

Visual Inspection

Chip Carrier(Tray)에 옮겨 담은 양품chip의 외관 검사 기준에 의거, 양/불 분류하는 공정

-

12

Packing

최종 분류된 양품Chip의 출하를 위한 진공포장, 내포장, 외포장을 하는 공정

introduction

웨이퍼 상태에서 여러가지의 검사를 통해

각 칩들의 상태를 확인하는 과정 Chip Probe Test

LB Semicon에서 진행하는 EDS(Electrical Die Sorting)공정은 개별 칩들의 품질 특성이 목표 수준에 도달했는지 확인하는 공정으로써, Wafer 상태 반도체 칩의 양품/불량품을 선별하고, 설계 단계에서의 문제점을 수정하며, 불량 칩을 미리 선별하여 후속 공정들의 작업 효율을 향상하는 목적으로 운영됩니다. 반도체 칩의 목적에 따라 디바이스 타입을 분류하고 각 칩의 특성에 맞는 전용 Tester를 이용하여 칩의 전기적 성능,품질 검사를 수행합니다.

이 과정에서 Auto Wafer Prober를 이용하여 자동으로 안전하고 신속하게 개별 칩의 테스트를 진행할 수 있게 됩니다.

테스트는 온도, 속도, 동작 테스트의 3가지로 분류할 수 있습니다.

온도별 테스트는 실제 칩이 사용될 때 다양한 온도 환경에서 동작되어야 하기 때문에 저온(Cold, -40℃)에서부터 고온(Hot, 125℃)까지 조건별로 인가하여 테스트합니다. 속도별 테스트는 제품의 동작 속도를 측정하는데, 반도체는 자체의 동작 속도도 중요하지만, 주변 기기와의 통신 속도 또한 중요하기 때문에 칩의 사양에 맞는 여러 환경의 속도 테스트가 중요합니다. 동작 테스트는 DC, AC, 기능(Function) 테스트로 구별할 수 있고 각각의 항목은 전류or전압, 아날로그 특성, 각 고유 칩 기능의 정상 동작을 확인합니다.

-

01 IAQ

-

02 P-TEST

-

03 INKING

-

04 SCOPE V/I

-

05 DOC.

INSPECTION -

06 QC GATE

(OGI) -

07 PACKING

(QPI) -

08 Shipping &

Back-end

Features

화면을 좌우로 스와이프하여 확인하여 주세요.| Application | Vendor | Model |

Specification (Pin mux, Pattern mux) |

Remark |

|---|---|---|---|---|

| DDI | Advantest | T6372(ND2) | 437.5MHz | - |

| T6373(ND3) | 437.5MHz | HSIF : 1.25GHz | ||

| T6391(ND4C) | 800MHz | UHSIF : 1.35GHz ~ 2.0GHz(License) | ||

| T6391S(ND4ST) | 800MHz | UHSIF : 2.0GHz ~ 3.25GHz(License) | ||

| Yokogawa | TS670 | - | UVI : 2.0A | |

| ST6730A | 375MHz | NSIO | ||

| ST6731A | 1.25GHz | GSIO | ||

| PMIC | Eagle | ETS-364B | 66MHz | - |

| Advantest | T2000-IPS | 250MBps | - | |

| T2000-IPS/EPP | 250Mbps/800Mbps/1Gbps | - | ||

| T2000-IPS 52TH | 1Gbps | GPWGD | ||

| CIS | Advantest | T2000-ISS/32 | 800Mbps | 1.2G Capture Module |

| T2000-ISS/64P | 1Gbps | 4.8G Capture Module | ||

| SOC | Teradyne | Ultra-FLEX | 1600Mbps | - |

Re-configuration Process

Sawing 처리된 Chip에 대하여 Sorting Issue 발생 or Test Program Debugging Re-Test 필요 시,

Loss를 최소화하여 Wafer Level Chip Test를 실시하는 공정 서비스를 제공 하고 있습니다.

- Chip on Tray

- Chip on Blue Tape(Ring Frame)

- Re-Test

- 2200 evo-Key Features(Re-con)

- Specifications FP 3000(Test)

DDI Test System

DDI Test System

DDI Test System

DDI Test System

PMIC Test System

PMIC Test System

CIS Test System

CIS Test System

SoC Test System

SoC Test System